The Address Translation Service (ATS) is a crucial process in the Peripheral Component Interconnect Express (PCIe) 6.0 architecture. It plays a pivotal role in ensuring that different processes or applications running on a system do not interfere with each other's memory space. Each process operates within its virtual address space, which is subsequently translated into a physical address. This mechanism is essential for maintaining system stability and preventing memory conflicts.

ATS, when accompanied by Process Request Identifiers (PRIs) and Process Address Space Identifiers (PASIDs) in PCIe 6.0, significantly enhances the capabilities of the device. However, these enhancements also increase the complexity of creating and debugging test scenarios.

The verification strategy should focus on ensuring the robustness and reliability of the enhanced ATS functionality in PCIe environments. It involves a systematic approach to testing different scenarios, including functional testing, performance testing, and stress testing. The goal is to identify and address potential issues early in the development process, reducing the risk of defects and ensuring a smooth user experience.

This blog, the first in its series, covers the requirements for ATS and various components proposed in the PCIe protocol generations. Subsequent blogs in this series will cover valuable insights into the challenges and strategies involved in verifying address translation in PCIe 6.0.

Introduction on Address Translations

Address translation is the process of converting a virtual address, which is a logical address used by a program, into a physical address, which is the actual location of the data in memory. The address translation can be performed by two different units, which maintain the translation mapping:

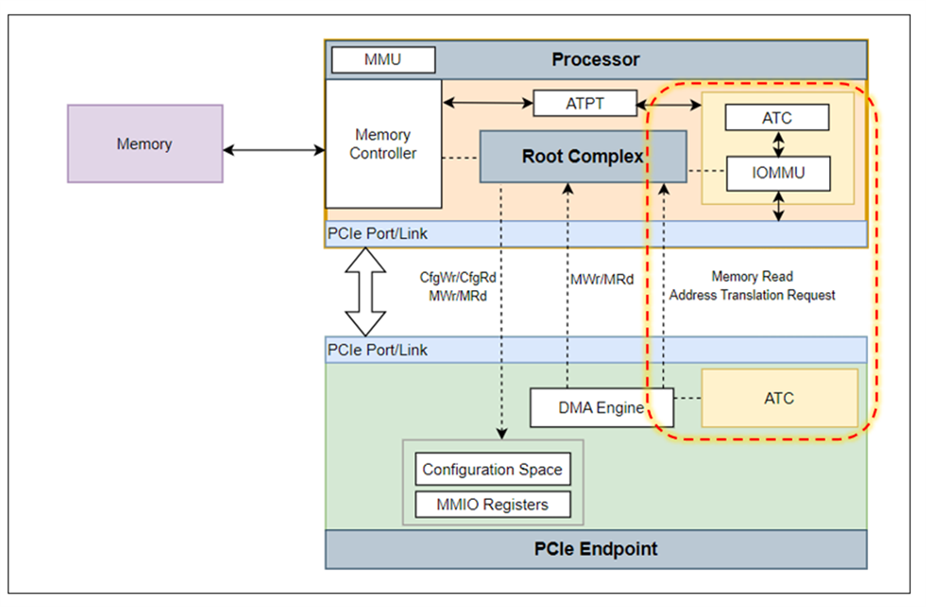

- Memory Management Unit (MMU) – converts CPU Virtual Address into Physical Address

- Input/Output Memory Management Unit (IOMMU) – converts Device I/O Virtual Address into Physical Address

Address Translation Process

The address translation process is as follows:

- When a program references a memory location, the virtual address is sent to the MMU.

- The MMU checks its translation lookaside buffer (TLB) to see if the virtual address has been translated recently.

- If the virtual address is found in the TLB, the physical address is returned to the processor.

- If the virtual address is not found in the TLB, the MMU performs a page table walk to find the physical address.

- The physical address is then returned to the processor.

Benefits of Address Translation

Both MMU and IOMMU keep a record of address translations initiated by the CPU and devices, respectively. Here are some of the benefits of address translation:

- Memory Protection: Address translation allows the operating system to protect memory by preventing unauthorized access to certain areas of memory. This is essential for ensuring the security of the system and its data.

- Virtual Memory: Address translation enables the use of virtual memory, which allows the operating system to manage memory more efficiently. Virtual memory allows the operating system to create the illusion of a larger amount of physical memory than is available, by using a portion of the hard disk as a temporary storage area for data that is not currently being used.

- Cache coherency: Address translation allows the operating system to maintain cache coherency, which is a technique that ensures that all copies of a data item in memory are consistent.

- Device Isolation: Address translation helps to isolate devices from each other, which can prevent conflicts and improve system stability.

- Reduced Processing Overhead: To reduce the overhead of address translations performed in the processor, the address translation caching (ATC) in the device is introduced which is used along with ATS. The ATC is maintained in devices that provide address translation mapping when accessing Host memory. ATS provides a way for Endpoints (EPs) to maintain an ATC consistent with the Address Translation and Protection Table (ATPT) maintained in the Root Complex (RC).

ATS Components

Translation Agent (TA), which can be either IOMMU or MMU, is managed by Hypervisor/Software. It translates addresses on behalf of the host for PCIe devices, ensuring security and granting access to Host memory for DMA transactions. The TA uses data structures like page tables and communicates with RC to generate successful or unsuccessful completion of requested translation TLP.

Address Translation Protection Table (ATPT) is a data structure used to store page tables for address translation. It contains the set of address translations accessed by a Translation Agent (TA) to process PCIe requests. DMA Read and Write requests are translated through a combination of the Routing ID and the address contained within a PCIe transaction.

Address Translation Cache (ATC) is a cache in the device or Endpoint that stores translations between virtual and physical addresses in virtual memory systems. It acts as a cache layer that speeds up the translation process by storing recent virtual to physical address mappings. The ATC improves system performance by reducing the latency of the CPU. Each ATC entry must be filled via an ATS Translation Completion in response to a Function issuing an ATS Translation Request. The ATC is present only in Physical Functions.

System Architecture Block Diagram

Summary

ATS is a feature in the PCIe standard that allows an I/O device to perform its own address translations without relying on the host's CPU. This can help to reduce latency and improve overall system performance.

ATS-supporting devices connect a direct memory access-capable (DMA-capable) I/O bus to the main memory. When an ATS-enabled device needs to access memory, it can use the ATS feature to translate the virtual address of the memory location into a physical address. This translation is done in hardware, which is much faster than if the translation were done in software by the CPU.

There are several benefits to using ATS. First, it can reduce latency. When an I/O device needs to access memory, it does not have to wait for the CPU to perform the address translation. This can improve the performance of applications that require fast access to memory. Second, ATS can improve overall system performance. By reducing the load on the CPU, ATS can free up the CPU to perform other tasks. This can improve the performance of the entire system.

Address translation is an essential part of modern computer systems. It provides several benefits, including memory protection, virtual memory, and cache coherency.

Further Information

- PCI Express® Base Specification Revision 6.2, Version 1.0

- To learn more about Cadence PCIe Verification IP, see VIP for PCI Express