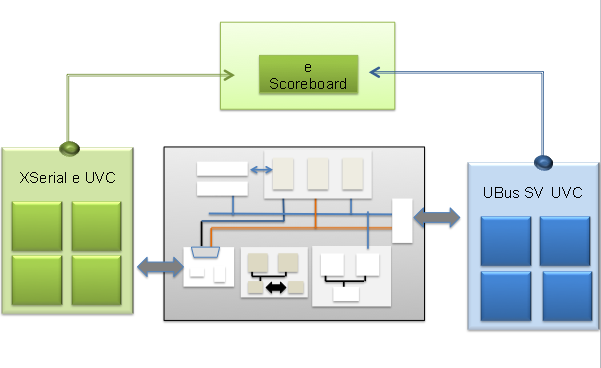

In the previous blog post, we demonstrated connecting a checker implemented in SystemVerilog to a monitor implemented in e.

In this post, we will show a fast way for adding a system-level data checker – using the UVM Scoreboard. The UVM Scoreboard is an open-source framework, implemented in e, and is released as part of the UVM e Library.

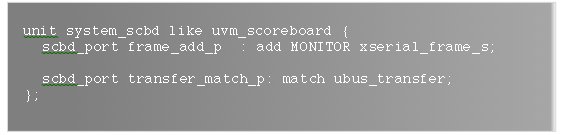

For adding a scoreboard to our XSerial-to-UBus environment, we define a scoreboard with one add port handling XSerial data items and one match port handling UBus transfers. scbd_port is a macro, it adds to the scoreboard unit a tlm_analysis port of requested type. The following code defines a scoreboard unit getting xserial_frame_s and storing them in the add queue, and when getting ubus_transfers, it searches the queue for a match.

For passing items using TLM ports, we use UVM-ML –

- If you haven’t already, download and install UVM-ML from Accelera UVMWorld

- When compiling the environment, use the required UVM_ML flags. The best way for adding the required flags is using the option files that are provided within the UVM-ML library.

For example, running an environment containing e and SystemVerilog UVCs:

irun ./test.sv \

-f ${UVM_ML_HOME}/ml/run_utils/ml_options.32.f \

-f ${UVM_ML_HOME}/ml/run-utils/sv_options.32.f \

-f ${UVM_ML_HOME}/ml/run_utils/e_options.32.f \

-uvmtop SV:svtest -uvmtop e:./top.e \

-exit

See the UVM-ML User Guide, residing under the docs directory in the UVM-ML library, for the detailed description of compiling multi-language environments.

Passing structs via the TLM ports is achieved by serializing the transaction content, sending it to the connected port, and de-serializing it there. This process requires two things:

- Need to know which type mapped to which type in the other language (known as “type mapping”)

- The serialization and de-serialization needs to match, in order to get the same transaction on each side

For e-to-e ports, all this is implemented automatically. So for passing items from the e XSerial monitor to the Scoreboard, all we have to do is bind the monitor’s port to the scoreboard’s frame_add_p.

For connecting the SystemVerilog monitor to the e scoreboard, we have to implement the required type –ubus_transfer - in e, and implement the serialization and de-serialization. The fastest way to do so is using IES mltypemap. We run it on the code containing the definition of the requested struct, and it creates e and SystemVerilog files, containing all code that is required for passing the struct between SystemVerilog and e.

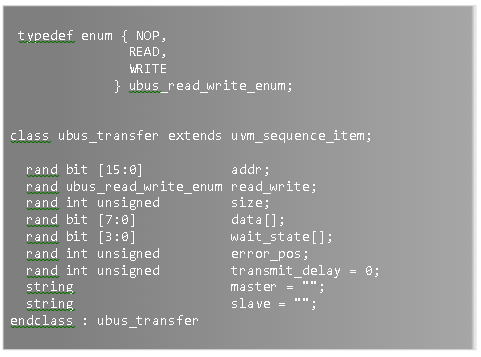

If the ubus_transfer definition is as follows:

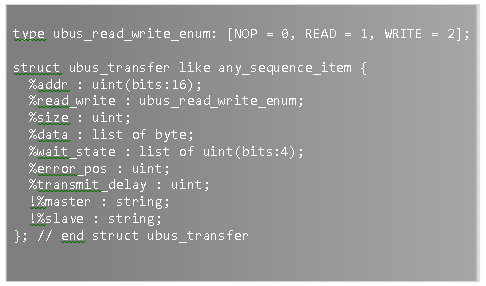

Running on it mltypemap will result in this e code:

Note how mltypemap creates conversion also for required type, ubus_read_write_enum in this example.

After defining the scoreboard and the serialization code, all that's left is connecting the ports. The connection can be implemented either in SystemVerilog or in e. In our example we implement it in e, using connect_names(). For connecting ports of two languages, they have to be registered. SystemVerilog ports are registered using UVM-ML TLM register(), and e ports are bound to external.

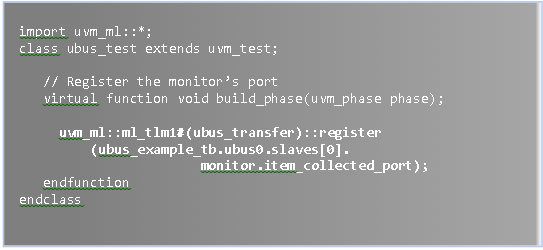

In SystemVerilog:

- Include the UVM-ML library

- Register the monitor's port to UVM-ML

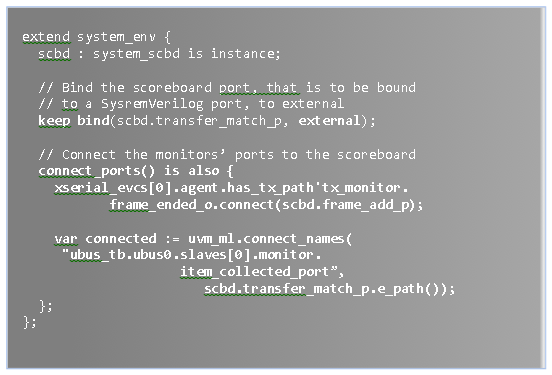

in e:

- Instantiate the scoreboard

- Bind the port that is connected to a SystemVerilog port to external

- Connect the ports:

- e-to-e ports connect using connect()

- e-to-SV ports connect using UVM-ML connect_names()

As you can see, the amount of code required for passing data from e to SystemVerilog and vice versa is quite small:

- Match the types and implement the serialization:

- mltypemap automates this task

- Register the SystemVerilog port to UVM-ML

- Bind the e port to external

- Connect the ports, using UVM-ML connect_names()

See detailed description and examples of passing items via TLM ports in UVM-ML examples, User Guide, and Reference Manual.

For mltypemap– see CadenceHelp.

In the next post in this series - Multi-Language Verification Environment – Multi-Language Hierarchy – we will show how we can instantiate e units within SystemVerilog components.

Happy verification,

Efrat Shneydor