In the previous posts in this series on Multi-Language Verification Environment, we created a multi-language environment containing UVCs implemented in e and SystemVerilog.

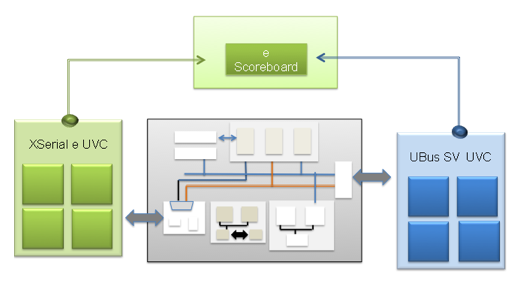

This environment is functional—exercising the DUT interfaces containing one system-level checker—but something is flawed in this picture. We have UVCs instantiated side by side, rather than in their “natural” location in the hierarchy. In a UVM environment, we want the system-level component to contain several sub-components. This is the recommended architecture, and we want to implement it, regardless of the language in which the UVCs are implemented.

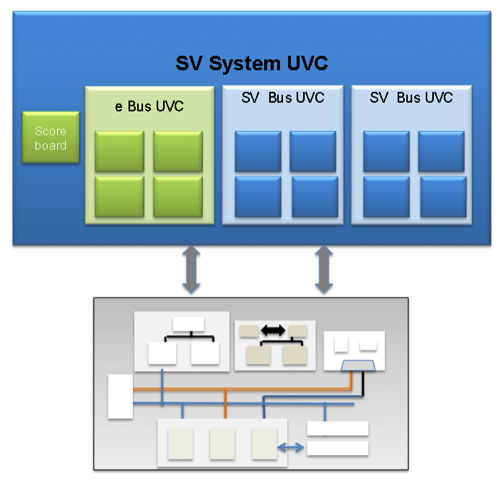

What we really want is something like this:

Creating such a Unified Hierarchy environment, with SystemVerilog component instantiating e units, and/or an e unit containing SystemVerilog components, is achievable when using UVM-ML.

(If you still haven’t installed UVM-ML, it is available at Accelera UVMWorld: http://forums.accellera.org/files/file/65-uvm-ml-open-architecture/.)

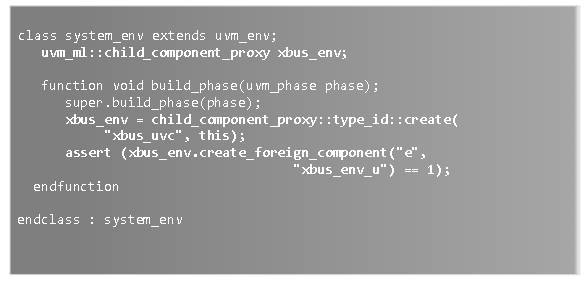

To instantiate a component implemented either in another language, we have to instantiate a child proxy. For instantiating an e unit within a SystemVerilog component:

- Define a variable of type uvm_ml::child_component_proxy

- Or of a class extending child_component_proxy

- Allocate it using child_component_proxy::type_id::create()

- Instantiate the foreign language (e) component, using create_foreign_component()

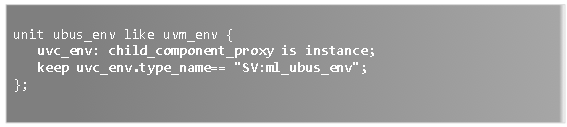

For instantiating a SystemVerilog component within an e unit:

- Define a field of the predefined type child_component_proxy

- Or of a type derived from child_component_proxy

- Constrain the field’s type_name to the name of the type in the foreign language you want to instantiate

This ability to instantiate components in their intuitive location in the hierarchy regardless of the implementation language gives us the capability not only to create the environment in the “right” architecture, but also the important ability of configuration.

With uvm_config, you can configure sub-components implemented either in e or in SystemVerilog. uvm_config is implemented in UVM-ML for SystemVerilog and in Specman for e.

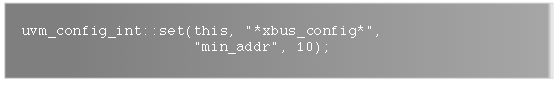

The following SystemVerilog code, for example, configures all sub components—implemented either in e or in SystemVerilog—whose path contains the string xbus_config. If they have a field named min_addr, it is configured to be 10.

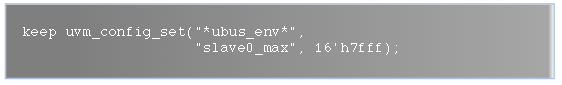

And this e code configures all sub-components implemented in e or in SystemVerilog that its path contains the string ubus_env. If they have a field named slave0_max, it is set to 0x7fff.

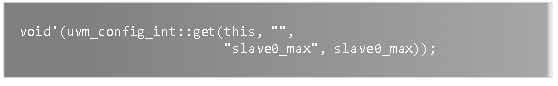

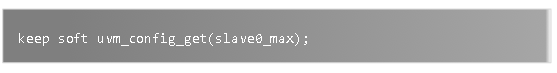

The UVM-ML configuration is analogous to the UVM SystemVerilog configuration. The sub-component has to get the value, in order for configuration to take place. The SystemVerilog component can call uvm_config_*::get(), and in e– constrain to uvm_config_get()–.

SV:

e:

Examples of Unified Hierarchy and Multi-Language configuration are available in the UVM-ML library, and in its user guide. UVM-ML is available in Accelera UVMWorld at http://forums.accellera.org/files/file/65-uvm-ml-open-architecture/.

The next blog in this series—Debugging Multi Language Verification Environments—will show main techniques and commands for debugging multi-language verification environment.

Happy verification,

Efrat Shneydor